DNP erreicht eine Linienmusterauflösung von 10 nm auf einem Nanoimprint-Template für hochmoderne Halbleiter

DNP erreicht eine Linienmusterauflösung von 10 nm auf einem Nanoimprint-Template für hochmoderne Halbleiter

- Unterstützt Halbleiter der 1,4-nm-Generation und senkt die Herstellungskosten sowie den Energieverbrauch -

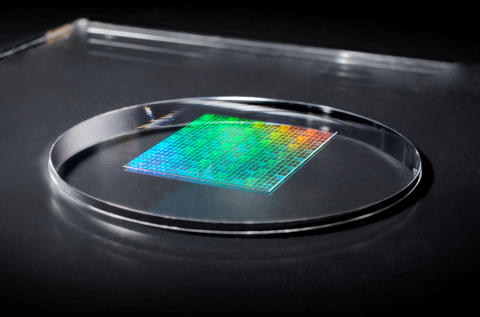

TOKIO--(BUSINESS WIRE)--Dai Nippon Printing Co., Ltd. (DNP, TOKYO:7912) hat heute die Entwicklung eines Nanoimprint-Lithographie (NIL)-Templates mit einer Leiterbahnbreite von 10 Nanometern (nm: 10-9 Meter) angekündigt. Das neue Template ermöglicht die Erstellung von Strukturen für Logikhalbleiter, die der 1,4-nm-Generation entsprechen, und erfüllt die Anforderungen hinsichtlich der Miniaturisierung modernster Logikhalbleiter.

Hintergrund und Ziele

Angesichts des Trends zu immer komplexeren Geräten in den letzten Jahren ist die Nachfrage nach einer noch stärkeren Miniaturisierung modernster Halbleiter gestiegen, was zu Fortschritten in der Extrem Ultra-Violett (EUV)-Lithografie-basierten Produktion geführt hat. Allerdings erfordert die EUV-Lithografie erhebliche Investitionen, sie ist mit einem hohen Energieverbrauch verbunden und verursacht hohe Betriebskosten für den Aufbau von Produktionslinien und für den Expositionsprozess.

DNP entwickelt seit 2003 NIL-Templates und hat mit Erfolg umfangreiches Fachwissen im Bereich der hochpräzisen Strukturierung erworben.

Mit dieser neuesten Entwicklung hat DNP ein NIL-Template mit einem 10-nm-Linienmuster entwickelt. Es kann einen Teil des EUV-Lithografieprozesses ersetzen und die Herstellung modernster Logikhalbleiter für Kunden erleichtern, die über keinen EUV-Lithografie-Produktionsprozess verfügen.

Die wichtigsten Merkmale

- DNP hat erfolgreich das neue NIL-Template mit einer Leiterbahnbreite von 10 nm realisiert, indem es Self-Aligned Double Patterning (SADP) einsetzte. Dadurch wird die Strukturdichte durch Filmabscheidung und Ätzen einer mit dem Lithografiegerät erzeugten Struktur verdoppelt.

- Darüber hinaus reduziert die Technologie auch den Stromverbrauch im Expositionsprozess der modernen Halbleiterfertigung. Durch den Einsatz einer energiesparenden Verarbeitungstechnologie für ultrafeine Halbleiter unter Verwendung von NIL ist es nun möglich, den Stromverbrauch auf etwa ein Zehntel der derzeit verfügbaren Expositionsprozesse wie Argonfluorid (ArF)-Immersion und EUV zu senken.

Ein Blick in die Zukunft

Wir haben mit der Evaluierungsarbeit für NIL-Templates begonnen und wollen 2027 die Massenproduktion aufnehmen. DNP wird die Weiterentwicklung von NIL-Templates vorantreiben und die Produktionskapazitäten ausbauen, um der wachsenden Nachfrage gerecht zu werden. Der Plan sieht eine Steigerung des NIL-Umsatzes auf 4 Milliarden Yen im Geschäftsjahr 2030 vor.

DNP, das im Jahr 1876 gegründet wurde, hat sich zu einem weltweit führenden Unternehmen entwickelt, das auf Drucktechnologie basierende Lösungen einsetzt, um neue Geschäftsmöglichkeiten zu erschließen, dabei die Umwelt zu schützen und eine bessere Welt für alle zu schaffen. Dank unserer Kernkompetenzen in den Bereichen Mikrofabrikation und Präzisionsbeschichtungstechnologie können wir Produkte für die Märkte Display, elektronische Geräte und optische Folien anbieten.

Die Ausgangssprache, in der der Originaltext veröffentlicht wird, ist die offizielle und autorisierte Version. Übersetzungen werden zur besseren Verständigung mitgeliefert. Nur die Sprachversion, die im Original veröffentlicht wurde, ist rechtsgültig. Gleichen Sie deshalb Übersetzungen mit der originalen Sprachversion der Veröffentlichung ab.

Contacts

Ansprechpartner für Medien

DNP: Yusuke Kitagawa, +81-3-6735-0101

kitagawa-y3@mail.dnp.co.jp