DNP atteint une résolution de ligne de 10 nm sur une matrice de nanoimpression pour les semiconducteurs de pointe

DNP atteint une résolution de ligne de 10 nm sur une matrice de nanoimpression pour les semiconducteurs de pointe

- Prend en charge les semiconducteurs de génération 1,4nm et réduit les coûts de fabrication et la consommation d'énergie -

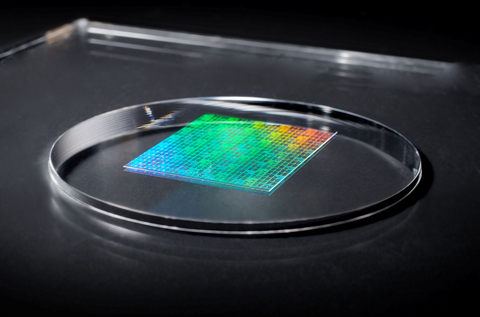

TOKYO--(BUSINESS WIRE)--Dai Nippon Printing Co., Ltd. (DNP, TOKYO:7912) annonce aujourd'hui le développement d'une matrice de lithographie par nanoimpression (NIL) avec une largeur de ligne de circuit de 10 nanomètres (nm : 10-9 mètre). La nouvelle matrice permet de modéliser des semiconducteurs logiques équivalents à la génération 1,4nm et répond aux besoins de miniaturisation des semiconducteurs logiques de pointe.

Contexte et objectifs

Conformément au passage à des dispositifs plus sophistiqués observé ces dernières années, des demandes ont émergé pour une miniaturisation encore plus grande des semiconducteurs de pointe, conduisant à des progrès dans la production basée sur la lithographie extrême ultraviolet (EUV). La lithographie EUV, cependant, nécessite d'importants investissements en capital, la consommation d'énergie et les coûts d'exploitation dans les lignes de production des bâtiments et le processus d'exposition.

Depuis 2003, DNP développe des matrices NIL et a acquis un vaste savoir-faire en matière de modélisation de haute précision.

Avec cette nouvelle avancée, DNP a développé une matrice NIL avec un motif de ligne de 10 nm. Cette approche est capable de remplacer une partie du processus de lithographie EUV, facilitant la fabrication de semiconducteurs logiques de pointe pour les clients qui n'ont pas de traitement de production de lithographie EUV.

Caractéristiques clés

- DNP a réalisé la nouvelle matrice NIL avec une largeur de ligne de circuit de 10 nm en tirant parti du double motif auto-aligné (SADP), qui double la densité de motif par dépôt de film et gravure d'un motif formé par le dispositif de lithographie.

- La technologie réduit également la consommation d'énergie dans le processus d'exposition de la fabrication de semiconducteurs de pointe. Grâce à une technologie de traitement économe en énergie pour les semiconducteurs ultrafins utilisant le NIL, il est désormais possible de réduire la consommation d’énergie à environ un dixième des processus d’exposition actuellement disponibles, tels que l’immersion en fluorure d’argon (ArF) et l’EUV.

Perspectives d'avenir

Nous avons commencé le travail d'évaluation pour les matrices NIL, et nous visons à commencer la production de masse en 2027. DNP fera progresser le développement des matrices NIL et renforcera la capacité de production pour répondre à la demande croissante, en ciblant des ventes de quatre milliards de yens à l'exercice 2030 pour les matrices NIL.

DNP a été créé en 1876 et est devenu une entreprise mondiale de premier plan qui exploite des solutions d'impression pour créer de nouvelles opportunités commerciales tout en protégeant l'environnement et en créant un monde plus dynamique pour tous. Nous capitalisons sur les compétences de base dans la microfabrication et la technologie de revêtement de précision pour fournir des produits pour les marchés de l'affichage, des appareils électroniques et des films optiques.

Le texte du communiqué issu d’une traduction ne doit d’aucune manière être considéré comme officiel. La seule version du communiqué qui fasse foi est celle du communiqué dans sa langue d’origine. La traduction devra toujours être confrontée au texte source, qui fera jurisprudence.

Contacts

Contact avec les médias

DNP : Yusuke Kitagawa, +81-3-6735-0101

kitagawa-y3@mail.dnp.co.jp