DNP開發出用於下一代半導體封裝的主要元件——中介層電路板

DNP開發出用於下一代半導體封裝的主要元件——中介層電路板

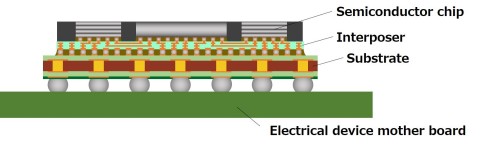

東京--(BUSINESS WIRE)--(美國商業資訊)-- (美國商業資訊)--Dai Nippon Printing Co., Ltd. (DNP, TOKYO:7912)開發出一種中介層電路板(interposer),這是一種將多個晶片和基板進行電氣連接的高性能中間元件,有望在下一代半導體封裝中發揮關鍵作用。

DNP還加入了Jisso Open Innovation of Tops 2 (JOINT2),目標是為2024年的量產進行進一步的功能開發。JOINT2是一個由12家從事半導體封裝材料、基板和設備開發的公司所組成的協會。Showa Denko Materials Co., Ltd.是該協會的管理公司,被新能源和工業技術開發組織(NEDO)選入後5G資訊通訊系統增強型基礎建設的研發專案。

DNP研究與業務開發中心的 Ryoichi Ohigashi表示:「透過與其他參與JOINT2的公司合作,DNP將加速中介層電路板具體功能的進一步研發,並推動旨在2024年實現量產的措施。我們還將推動下一代半導體封裝技術的開發。」

背景

半導體產品向更高功能、更快速度和更低功耗的轉變,需要透過使用微影技術來實現半導體的微型化技術。然而,由於製程的複雜性和高成本,進一步的微型化據稱正在迅速接近極限。為了克服這些挑戰,需要以下一代半導體封裝技術為重點,該技術透過在中介層電路板表面以高密度安裝多個晶片(例如CPU、AI處理器和記憶體)來提高處理速度。

特性

該中介層電路板克服了佈線電阻增加和佈線之間絕緣電阻下降的問題,可實現尖端半導體封裝所需要的高性能。

DNP製造用於奈米壓印微影的範本,這是一種下一代圖案轉移技術,採用以印刷製程為基礎的微細加工技術。我們還透過感測器的MEMS代工服務廣泛地拓展業務。在這次開發過程中,我們將透過上述業務所開發的玻璃和矽基板加工應用於先進的封裝技術,同時還應用了處理技術和精細佈線形成技術。

關於DNP

自1876年以來,DNP一直是連接個人與社會的列印解決方案的全球領導者,致力於提供新的價值。我們利用自身在印刷和資訊方面的專有優勢,提出支援發展以人為本的資訊社會的解決方案,包括瞄準下一代通訊的電子元件,以及促進物聯網資訊安全的平臺。

https://www.dnp.co.jp/eng/news/detail/10161795_2453.html

免責聲明:本公告之原文版本乃官方授權版本。譯文僅供方便瞭解之用,煩請參照原文,原文版本乃唯一具法律效力之版本。

Contacts

DNP: Yusuke Kitagawa, 81-3-6735-0101

kitagawa-y3@mail.dnp.co.jp