DNP实现适用于超2nm一代的EUV光刻光掩模精细图案分辨率

DNP实现适用于超2nm一代的EUV光刻光掩模精细图案分辨率

开始供应用于下一代半导体的高NA EUV光掩模样品

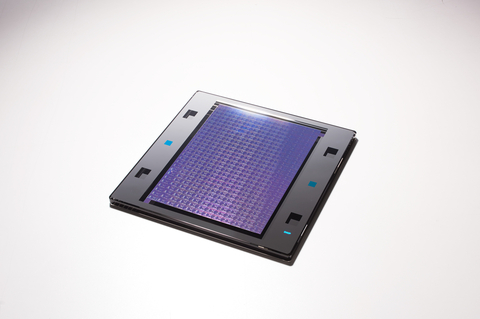

东京--(BUSINESS WIRE)--(美国商业资讯)-- Dai Nippon Printing Co., Ltd. (DNP, TOKYO: 7912) 成功实现超2nm(nm:10-9米)一代1逻辑半导体光掩模所需的精细图案分辨率,支持半导体制造领域的尖端工艺——极紫外光(EUV)光刻技术。

DNP还完成了兼容高数值孔径2光掩模的标准评估,而超2nm的下一代半导体正在考虑采用高数值孔径技术。同时DNP已开始提供评估光掩模。高NA EUV光刻技术能够以比以前更高的分辨率在硅晶圆上形成精细图案,并有望实现高性能、低功耗的半导体。

[开发]

- 要实现超2nm一代EUV光刻的光掩模,需要图案比3nm一代小20%。这不仅指图案的大小和形状,还指在相同掩模的表面上解析所有类型精细图案所需的技术。这不仅包括标准的直线和矩形图案,还包括日益复杂的弯曲图案。 DNP在既定的3nm一代制造工艺基础上反复改进,达到了超2nm一代所需的图案分辨率

- 与标准EUV光刻相比,用于高NA-EUV光刻的光掩模需要更高的精度和更精细的加工。 DNP建立并优化了与传统EUV光刻光掩模不同的制造工艺流程。

[展望未来]

DNP将继续建立生产技术,目标是在2027财政年度开始大规模生产2nm一代逻辑半导体的光掩模。

我们还将继续与imec合作,推动光掩模制造技术的发展,并以实现1nm一代为目标。

1: 符合IRDS标准

2: 数值孔径(NA)是表示光学系统亮度和分辨率的数字。高NA是指将EUV曝光设备的镜头NA从传统的0.33扩大到0.55。

关于DNP

DNP成立于1876年,现已发展成为全球领企业。该公司利用基于印刷的解决方案来设计新商业机会,同时保护环境,为所有人创造更加生机勃勃的世界。我们利用在微细加工和精密涂层技术方面的核心竞争力,为显示器、电子设备和光学薄膜市场提供产品。 我们还开发了蒸汽腔体和反射阵列等新产品,为更加人性化的信息社会提供下一代通信解决方案。

免责声明:本公告之原文版本乃官方授权版本。译文仅供方便了解之用,烦请参照原文,原文版本乃唯一具法律效力之版本。

Contacts

媒体联系人

DNP: Yusuke Kitagawa, +81-3-6735-0101

kitagawa-y3@mail.dnp.co.jp