DNP加速开发面向2纳米EUV光刻时代的光刻掩模版制造工艺

DNP加速开发面向2纳米EUV光刻时代的光刻掩模版制造工艺

- 作为Rapidus分包商参加NEDO研发项目 -

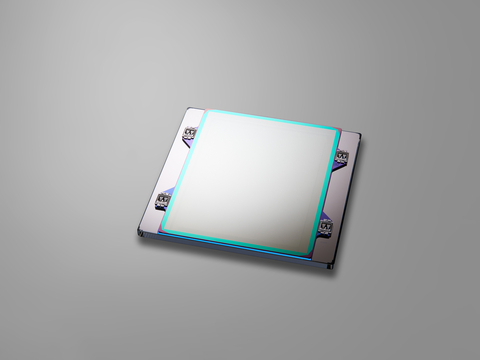

东京--(BUSINESS WIRE)--(美国商业资讯)-- Dai Nippon Printing Co., Ltd.(简称DNP,东京证券交易所:7912)开始研发面向2纳米逻辑半导体的光刻掩模版制造工艺,支持极紫外(EUV)光刻这一前沿的半导体制造技术。

DNP还将作为分包商向东京Rapidus Corporation (Rapidus)提供这种新开发的技术。Rapidus目前正参加日本新能源产业技术综合开发机构(NEDO)所发起的后5G信息通信系统增强基础设施研发项目。

[背景]

我们不断强化自己以高生产率和高质量生产先进半导体产品的能力。2016年,DNP 成为全球首家推出多光束掩膜写入工具(MBMW)的商业光刻掩模版制造商 。

2023年,我们完成了 面向3纳米EUV光刻制程的光刻掩模版制造工艺开发 ,并启动了2纳米制程技术的开发工作。面对行业对进一步微型化的要求,我们将开始全面开发面向2纳米EUV光刻时代的光刻掩模版制造工艺,包括在2024财年投入第二套和第三套光束掩膜光刻系统。

DNP计划在2024年财年投入第二套和第三套MBMW掩膜光刻系统,加速开发面向2纳米EUV光刻时代的光刻掩模版。

DNP将按照Rapidus的委托,作为分包商负责开发先进半导体制造技术,从而参与之前所提到的NEDO研发项目。

[未来展望]

到2025财年,DNP将完成面向2纳米逻辑半导体时代的光刻掩模版制造工艺开发,以支持EUV光刻技术。从2026财年开始,我们将努力建设生产技术,以在2027财年开始量产为目标。

我们还启动了针对2纳米及更先进制程的研发工作,并与总部位于比利时鲁汶的先进国际研究机构imec签署了协议,联合开展新一代EUV光刻掩模版。DNP将继续在国际半导体产业框架下推动与各种合作伙伴的联合开发工作,为促进日本半导体产业的发展贡献力量。

关于 DNP

DNP成立于1876年,现已成为全球领先的公司,利用印刷解决方案来发掘全新的商业机遇,同时注重保护环境并为所有人建设更富有活力的世界。我们运用在微细加工和精确涂装领域的核心优势,提供面向显示器、电子设备和光学膜市场的产品。我们还不断开发各种新产品,例如均热板和反射阵列,提供下一代通信解决方案,建设对人更友好的信息社会。

免责声明:本公告之原文版本乃官方授权版本。译文仅供方便了解之用,烦请参照原文,原文版本乃唯一具法律效力之版本。

Contacts

媒体垂询

DNP:Yusuke Kitagawa,+81-3-6735-0101

kitagawa-y3@mail.dnp.co.jp