Alphawave Semi展示面向高性能人工智能基础设施的3纳米硅验证24Gbps通用小芯片互连™ (UCIe™ ) 子系统

Alphawave Semi展示面向高性能人工智能基础设施的3纳米硅验证24Gbps通用小芯片互连™ (UCIe™ ) 子系统

成功的硅片初启扩大了硅片解决方案的领先地位,加速了人工智能连接和计算

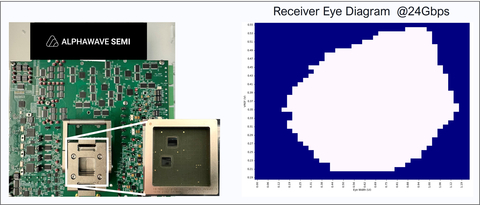

伦敦和多伦多--(BUSINESS WIRE)--(美国商业资讯)-- 全球技术基础设施高速连接和计算解决方案领域的领导者Alphawave Semi (LSE: AWE) 今天宣布,其首个小芯片连接硅平台已在台积电最先进的3纳米制程上成功初启。这一全新经过硅验证的通用小芯片互连 (UCIe™) 子系统扩大了Alphawave Semi在连接硅片方面的产品组合和领先地位,为一个强大、开放的小芯片生态系统铺平了道路,加速了高性能人工智能系统的连接和计算。最近,在加利福尼亚州圣克拉拉举行的小芯片峰会(Chiplet Summit)上,Alphawave Semi首次面向业界现场演示了采用台积电3纳米制程的24Gbps UCIe硅平台。

Alphawave Semi的3纳米UCIe完整物理层(PHY)+控制器子系统能够实现24Gbps的数据传输速率,以极低的功耗和低延迟提供高带宽密度。该解决方案符合最新的UCIe Revision 1.1规范,包括了一个高度可配置的芯片到芯片D2D控制器,支持流、PCIe® /CXL™、AXI-4、AXI-S、CXS和CHI协议。该子系统具有比特误码率(BER)健康监测功能,以确保稳定运行。物理层可配置为支持台积电的先进封装技术,如基底晶圆上芯片(CoWoS®)和整合式扇出晶圆级封装(InFO),从而最大限度地提高信号密度以及有机基板,以实现更具成本效益的解决方案。

“我们与Alphawave Semi的最新合作成果让我们倍感欣喜,即在台积电3纳米制程上提供经过硅验证的小芯片连接解决方案。”台积电设计基础设施管理部门主管Dan Kochpatcharin表示,“我们将继续与Alphawave Semi等我们的开放创新平台(Open Innovation Platform®, OIP)伙伴合作,旨在为高性能连接和计算硅片解决方案建立一个强大而开放的小芯片生态系统,以支持更多的人工智能应用。”

“我们的24Gbps UCIe子系统获得3纳米硅验证是Alphawave Semi的一个重要里程碑,这是我们专为超分频器和数据基础设施应用定制的小芯片连接平台的重要组成部分。” Alphawave Semi的IP产品营销副总裁Letizia Giuliano表示,“我们非常感谢台积电团队的杰出支持,并期待在台积电的尖端3纳米制程上加速我们共同客户的高性能小芯片设计。”

如需了解更多信息,请访问http://awavesemi.com。

客户可以通过在定制芯片和小芯片上集成UCIe、PCIe、CXL、Multi-Standard-Serdes和HBM等先进接口,受益于Alphawave Semi的应用优化IP子系统和先进的2.5D/3D封装技术。

关于 Alphawave Semi

Alphawave Semi是为全球技术基础设施提供高速连接和计算硅片的全球领先企业。随着数据量的爆炸性增长,Alphawave Semi的技术致力于解决一个关键需求——让数据传输得更快、更稳定,同时性能更高且功耗更低。作为一家垂直整合的半导体企业,我们的知识产权(IP)、定制硅片和连接产品已被全球顶尖客户在数据中心、计算、网络、人工智能、5G、自动驾驶汽车和存储等多个领域广泛应用。Alphawave Semi由一支在半导体知识产权授权领域经验丰富的专家技术团队于2017年成立,我们的使命是加速推进构建数字世界核心的关键数据基础架构。若要了解有关Alphawave Semi的更多信息,请访问:awavesemi.com。

Alphawave Semi 和 Alphawave-Semi 徽标是 AlphawaveIP Group plc 的商标。保留所有权利。

免责声明:本公告之原文版本乃官方授权版本。译文仅供方便了解之用,烦请参照原文,原文版本乃唯一具法律效力之版本。

Contacts

Gravitate PR(代表Alphawave Semi)

alphawave@gravitatepr.com