Panmnesia Announces Sample Availability of PCIe 6.0/CXL 3.2 Fabric Switch - The Industry’s First Fabric Switch Silicon Fully Implementing the CXL 3.2 Standard with Port-Based Routing (PBR) Support

Panmnesia Announces Sample Availability of PCIe 6.0/CXL 3.2 Fabric Switch - The Industry’s First Fabric Switch Silicon Fully Implementing the CXL 3.2 Standard with Port-Based Routing (PBR) Support

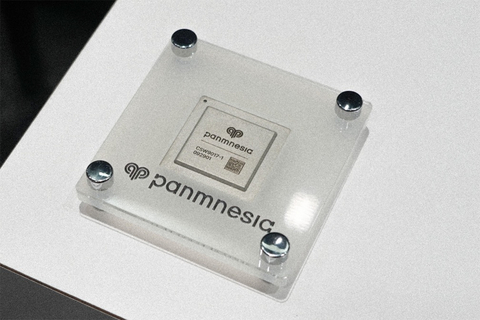

DAEJEON, South Korea--(BUSINESS WIRE)--Panmnesia, a pioneer in AI infrastructure link solutions, announced sample availability of its PCIe 6.0/CXL 3.2 Fabric Switch — the industry’s first CXL switch silicon supporting port-based routing (PBR). The company is currently in the process of providing switch silicon samples to early access partners.

Panmnesia’s switch is a hybrid solution that supports both PCIe Gen 6 and CXL 3.2 protocols on a single chip, while maintaining full backward compatibility with all previous PCIe and CXL generations. Fully implemented in strict accordance with the CXL 3.2/PCIe 6.0 specifications, it ensures complete standards compliance and seamless interoperability across all subprotocols. The switch can also operate in PBR mode and hierarchy-based routing (HBR) mode.

With these flexible routing options and a full-stack optimized architecture based on Panmnesia’s proprietary PCIe/CXL controller, the switch enables truly composable architecture that reduces CAPEX/OPEX while delivering high performance for large-scale, multi-device workloads — including AI applications such as DLRM, LLMs, and RAG, as well as HPC workloads like MPI-based scientific simulations.

“Today, we are excited to unveil our PCIe 6.0/CXL 3.2 Fabric Switch silicon sample,” said Dr. Myoungsoo Jung, CEO of Panmnesia. “We believe that this will be a meaningful milestone in our journey to redefine end-to-end AI infrastructure with our industry partners.”

Panmnesia’s PCIe/CXL Fabric Switch – Key Highlights

Panmnesia’s Fabric Switch connect numerous devices and enable efficient communication by offering the following differentiated features, allowing numerous devices in data centers and HPC environments to operate together as if they were a single, large-scale accelerator:

-

Unified Fabric without Manual Setup or Static Hierarchy:

Wherever they’re plugged in, Panmnesia’s Fabric Switches with PBR support form a self-organizing, topology-agnostic fabric that makes AI clusters to operate as a single unified accelerator.

-

Scalable Expansion without Relying on Slow Networks:

Panmnesia’s Switches can interconnect thousands of devices across multiple racks without incurring long network latency, thanks to support for cascading which enables multi-switch interconnection.

-

Accelerated Communication among Devices:

Supporting PCIe Gen6 data rates (64 GT/s), the Fabric Switches accelerate bulk data transfers. They also ensure cache coherency across devices by supporting all CXL subprotocols — CXL.cache, CXL.mem, and CXL.io — eliminating redundant copies.

-

Ultra-Low-Latency Data Access within Clusters:

Panmnesia’s Fabric Switches reduce overall data-access latency within clusters by minimizing hops through a high-fan-out architecture and lowering internal processing latency via the integration of Panmnesia’s proprietary CXL controller, featuring double-digit nanosecond latency.

Availability

Panmnesia’s PCIe 6.0/CXL 3.2 Fabric Switch Silicon is out now and early access partners can request samples and pilot systems. Panmnesia’s PCIe 6.0/CXL 3.2 Controllers integrated within the switch are silicon-proven, and customers can request variants designed for memory, accelerator, and CPU applications as standalone products. For more information about samples, products, and partnership, please contact through sales@panmnesia.com.

Contacts

Media Contact:

Name: Hanyeoreum Bae

Email: hyrbae@panmnesia.com

Website: https://panmnesia.com/